#### **General Description**

The MAX3935 is designed to drive an electro-absorption modulator (EAM) at data rates up to 10.7Gbps. It provides programmable output levels through externally adjustable bias and modulation currents. This EAM driver is fabricated with Maxim's in-house second-generation SiGe process.

The MAX3935 accepts differential ECL or ground-referenced CML clock and data-input signals. Inputs are terminated with on-chip  $50\Omega$  resistors. An input-data retiming latch can be used to reject input-patterndependent jitter if a clock signal is available.

The driver can modulate EAM devices at amplitudes up to 3.0Vp-p when the device impedance is  $50\Omega$ . Typical (20% to 80%) edge speeds are 34ps. The output has an on-chip  $75\Omega$  resistor for back termination. The MAX3935 allows for an EAM bias voltage up to 1.2V.

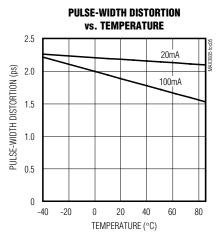

The MAX3935 also includes an adjustable pulse-width control circuit to precompensate for asymmetrical EAM characteristics.

## **Applications**

SONET OC-192 and SDH STM-64 Transmission Systems **DWDM**

Metro and Long Haul Transmitters Add/Drop Multiplexer

#### Features

- ♦ Single -5.2V Power Supply

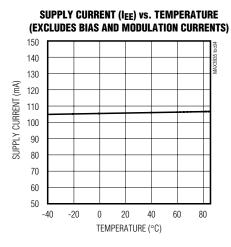

- ♦ Low 110mA Supply Current

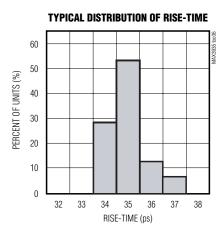

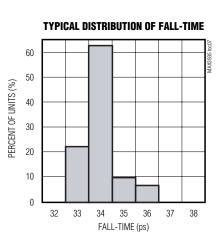

- ♦ 34ps Typical Rise/Fall-Time

- ♦ Up to 10.7Gbps (NRZ) Operation

- **♦ On-Chip Termination Resistors**

- ♦ Programmable Modulation Voltage Up to 3.0Vp-p

- ◆ Programmable EAM Bias Voltage Up to 1.2V

- **♦ Adjustable Pulse-Width Control**

- ♦ Selectable Data Retiming Latch

- **♦ Modulation Enable Control**

- **♦ ESD Protection**

### **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX3935EGJ | -40°C to +85°C | 32 QFN-EP*  |

<sup>\*</sup>Exposed pad

Pin Configuration appears at end of data sheet

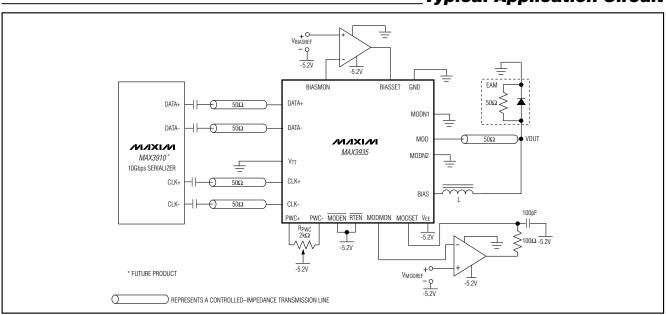

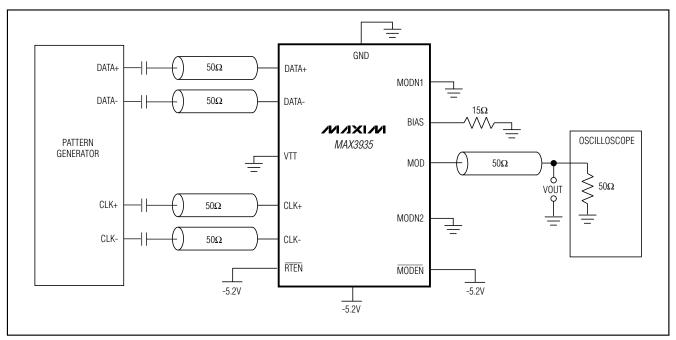

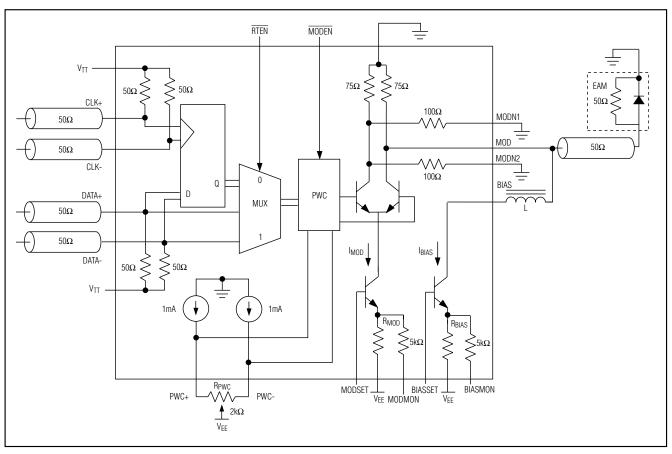

## **Typical Application Circuit**

†Covered by U.S. patent number 5,883,910.

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage V <sub>EE</sub> 6.0V to +0.5V V <sub>TT</sub> (V <sub>EE</sub> - 0.5V) to +0.5V DATA+, DATA- and CLK+, CLK(V <sub>TT</sub> - 1.2V) to the lower of (V <sub>TT</sub> + 1.2V) or +0.5V | MOD and BIAS Voltage                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| MODEN, RTEN, PWC+, and PWC(VEE - 0.5V) to +0.5V<br>MODSET and BIASSET Voltage(VEE - 0.5V) to (VEE + 1.5V)                                                                                           | Lead Temperature (soldering, 10s)+300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(VEE = -4.9V to -5.5V  $\pm 6\%$ , TA = -40°C to  $\pm 85$ °C. Typical values are at VEE = -5.2V, VCC =  $\pm 3.3$ V, IBIAS =  $\pm 16.7$ mA, IMOD =  $\pm 83.3$ mA, TA =  $\pm 25$ °C, unless otherwise noted.) (Note 1)

| PARAMETER                            | SYMBOL            | CONDITIONS                                  | MIN                   | TYP  | MAX                   | UNITS  |

|--------------------------------------|-------------------|---------------------------------------------|-----------------------|------|-----------------------|--------|

| Power-Supply Voltage                 | V <sub>EE</sub>   |                                             | -5.5                  | -5.2 | -4.9                  | V      |

| Power-Supply Current                 | I <sub>EE</sub>   | Excluding bias and modulation current       |                       | 106  | 140                   | mA     |

| Single-Ended Input Resistance        |                   | Input to V <sub>TT</sub>                    | 40                    | 50   | 60                    | Ω      |

| Bias Current-Setting Range           | I <sub>BIAS</sub> | IBIAS defined in Figure 3                   | 1.0                   |      | 40                    | mA     |

| Diag Coursest Catting Free           |                   | Bias current = 40mA, T <sub>A</sub> = +25°C | -10                   |      | +10                   | 0/     |

| Bias Current-Setting Error           |                   | Bias current = 1mA, T <sub>A</sub> = +25°C  | -5                    |      | +5                    | %      |

| Bias Sensing Resistor                | RBIAS             |                                             | 6.7                   | 7.5  | 8.3                   | Ω      |

| Bias Current Temperature             |                   | I <sub>BIAS</sub> = 40mA (Note 2)           | -480                  |      | +480                  |        |

| Stability                            |                   | I <sub>BIAS</sub> = 1mA                     |                       | -200 |                       | ppm/°C |

| Bias Off-Current                     |                   | BIASSET ≤ (V <sub>EE</sub> + 0.4V)          |                       |      | 0.05                  | mA     |

| MODEN and RTEN Input High            | VIH               |                                             | V <sub>EE</sub> + 2.0 |      |                       | V      |

| MODEN and RTEN Input Low             | V <sub>IL</sub>   |                                             |                       |      | V <sub>EE</sub> + 0.8 | V      |

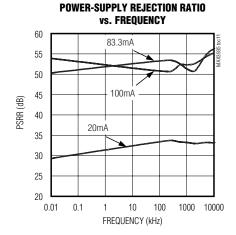

| Power-Supply Rejection Ratio         | PSRR              | f ≤ 10MHz, 100mVp-p<br>(Note 8)             |                       | 50   |                       | dB     |

| SIGNAL INPUT FOR V <sub>TT</sub> = 0 | •                 |                                             | •                     |      |                       | •      |

| Single-Ended Input                   | N/                | At high                                     |                       | 0    |                       |        |

| (DC-Coupled)                         | VIS               | At low                                      | -1.0                  |      | -0.15                 | V      |

| Single-Ended Input                   | N/                | At high                                     | +0.075                |      | +0.4                  | V      |

| (AC-Coupled)                         | VIS               | At low                                      | -0.4                  |      | -0.075                | V      |

### DC ELECTRICAL CHARACTERISTICS (continued)

(VEE = -4.9V to -5.5V  $\pm 6\%$ , T<sub>A</sub> = -40°C to +85°C. Typical values are at V<sub>EE</sub> = -5.2V, V<sub>CC</sub> = +3.3V, I<sub>BIAS</sub> = 16.7mA, I<sub>MOD</sub> = 83.3mA, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | SYMBOL          | CONDITIONS | MIN    | TYP  | MAX    | UNITS |

|-----------------------------------------|-----------------|------------|--------|------|--------|-------|

| Differential Input Swing (DC-Coupled)   | V <sub>ID</sub> |            | 0.3    |      | 2.0    | Vp-p  |

| Differential Input Swing (AC-Coupled)   | V <sub>ID</sub> |            | 0.3    |      | 1.6    | Vp-p  |

| SIGNAL INPUT FOR V <sub>TT</sub> = -1.3 | BV              |            |        |      |        |       |

| Input Common Mode                       | VICM            |            |        | -1.3 |        | V     |

| Cinala Endad Innut                      | Via             | At high    | -1.225 |      | -0.8   | V     |

| Single-Ended Input                      | VIS             | At low     | -1.8   |      | -1.375 | ]     |

| Differential Input Swing                | V <sub>ID</sub> |            | 0.3    |      | 2.0    | Vp-p  |

#### **AC ELECTRICAL CHARACTERISTICS**

(VEE = -4.9V to -5.5V  $\pm 6\%$ , TA = -40°C to  $\pm 85$ °C. Typical values are at VEE = -5.2V, VCC =  $\pm 3.3$ V, IBIAS =  $\pm 16.7$ mA, IMOD =  $\pm 83.3$ mA, TA =  $\pm 25$ °C, unless otherwise noted.) (Notes 1, 4, 5)

| PARAMETER                           | SYMBOL                          | CONDITIONS                                    | MIN  | TYP                   | MAX                   | UNITS     |

|-------------------------------------|---------------------------------|-----------------------------------------------|------|-----------------------|-----------------------|-----------|

| Input Data Rates                    |                                 | NRZ (Note 2)                                  |      | 10.7                  |                       | Gbps      |

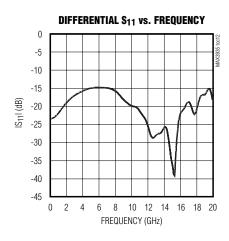

| Input Return Loss                   | RLIN                            | f ≤ 15GHz (Notes 2, 6)                        |      | 15                    |                       | dB        |

| Modulation Current-Setting<br>Range | IMOD                            | I <sub>MOD</sub> defined in Figure 3 (Note 7) | 20   |                       | 100                   | mA        |

| Modulation Current-Setting Error    |                                 | T <sub>A</sub> = +25°C                        | -10  |                       | +10                   | %         |

| Modulation Sensing Resistor         | RMOD                            |                                               | 2.7  | 3.0                   | 3.3                   | Ω         |

| Modulation Current Temperature      |                                 | I <sub>MOD</sub> = 100mA (Note 2)             | -550 |                       | +550                  | 10.00.000 |

| Stability                           |                                 | I <sub>MOD</sub> = 20mA                       |      | -200                  |                       | ppm/°C    |

| Modulation Off-Current              |                                 | MODSET ≤ (V <sub>EE</sub> + 0.4V)             |      |                       | 0.1                   | mA        |

| Output Back Termination<br>Resistor |                                 |                                               | 63.8 | 75.0                  | 86.3                  | Ω         |

| Output Edge Speed                   | t <sub>R</sub> , t <sub>F</sub> | $Z_L = 50\Omega$ , 20% to 80% (Note 3)        |      | 34                    |                       | ps        |

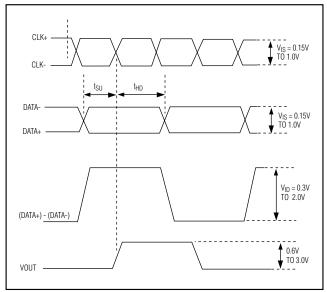

| Setup/Hold-Time                     | tsu, thd                        | Figure 2 (Notes 2, 3)                         |      | 8                     | ±25                   | ps        |

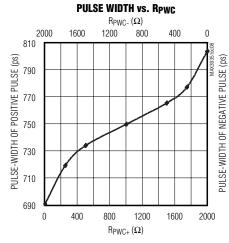

| Pulse-Width Adjustment Range        |                                 | $Z_L = 50\Omega$ , at 10Gbps (Notes 2, 3)     |      | ±60                   |                       | ps        |

| Pulse-Width Stability               |                                 | PWC+ and PWC- open (Notes 2, 3)               | -6   |                       | +6                    | ps        |

| Pulse-Width Control Input<br>Range  |                                 | For PWC+ and PWC-                             | VEE  | V <sub>EE</sub> + 1.0 | V <sub>EE</sub> + 2.0 | V         |

#### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{EE} = -4.9V \text{ to } -5.5V \pm 6\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C. \text{ Typical values are at } V_{EE} = -5.2V, V_{CC} = +3.3V, I_{BIAS} = 16.7mA, I_{MOD} = 83.3mA, I_{MOD} = 83.3mA$  $T_A = +25$ °C, unless otherwise noted.) (Notes 1, 4, 5)

| PARAMETER                   | SYMBOL | CONDITIONS | MIN | TYP  | MAX | UNITS             |

|-----------------------------|--------|------------|-----|------|-----|-------------------|

| Output Overshoot            | δ      | (Note 3)   |     | 1    |     | %V                |

| Driver Random Jitter        |        | (Note 3)   |     | 0.75 |     | psrms             |

| Driver Deterministic Jitter |        | (Note 5)   |     | 11   |     | ps <sub>p-p</sub> |

- **Note 1:** Specifications at -40°C are guaranteed by design and characterization.

- Note 2: Guaranteed by design and characterization.

- Note 3: Measured using a 10.7Gbps repeating 0000 0000 1111 1111 pattern.

- Note 4: AC characterization performed using the circuit in Figure 1.

- Note 5: Measured using a 10.7Gbps 213 -1 PRBS with 80 0's + 80 1's input data pattern.

- Note 6: For both data inputs DATA+, DATA- and clock inputs CLK+, CLK-.

- **Note 7:** Load impedance is  $50\Omega$  in parallel with an internal  $75\Omega$  termination.

- **Note 8:** PSRR =  $20 \times \log_{10} (V_{NOISE}(ON VCC)/(\Delta I_{MOD} \times 30\Omega))$ . Excludes the effect of the external op amp.

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

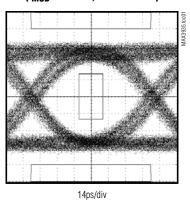

#### **OPTICAL EYE DIAGRAM** $(I_{MOD} = 100mA, 2^{13}-1 + 80CID)$

$(I_{MOD} = 100mA, 2^{13} - 1 + 80CID)$

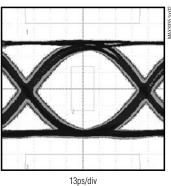

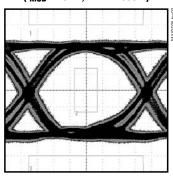

**ELECTRICAL EYE DIAGRAM**

**ELECTRICAL EYE DIAGRAM**  $(I_{MOD} = 20mA, 2^{13} - 1 + 80CID)$

13ps/div

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

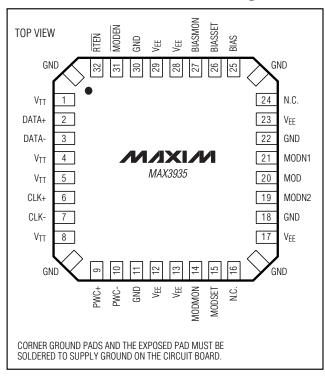

## **Pin Description**

| PIN                       | NAME            | FUNCTION                                                                                      |

|---------------------------|-----------------|-----------------------------------------------------------------------------------------------|

| 1, 4                      | VTT             | Termination Reference Voltage for Data Inputs                                                 |

| 2                         | DATA+           | Noninverting Data Input, with 50Ω On-Chip Termination                                         |

| 3                         | DATA-           | Inverting Data Input, with 50Ω On-Chip Termination                                            |

| 5, 8                      | VTT             | Termination Voltage for Clock Inputs                                                          |

| 6                         | CLK+            | Noninverting Clock Input for Data Retiming, with 50Ω On-Chip Termination                      |

| 7                         | CLK-            | Inverting Clock Input for Data Retiming, with 50Ω On-Chip Termination                         |

| 9                         | PWC+            | Positive Input for Modulation Pulse-Width Adjustment. Connected to VEE through RPWC.          |

| 10                        | PWC-            | Negative Input for Modulation Pulse-Width Adjustment. Connected to VEE through RPWC.          |

| 11, 18, 22, 30            | GND             | Ground                                                                                        |

| 12, 13, 17,<br>23, 28, 29 | V <sub>EE</sub> | Negative Supply Voltage                                                                       |

| 14                        | MODMON          | Modulation Current Monitor. ( $V_{MODMON} - V_{EE}$ ) / $3\Omega = I_{MOD}$ .                 |

| 15                        | MODSET          | Modulation Current Set. Connected to the output of an external op amp (see Design Procedure). |

| 16, 24                    | N.C.            | No Connection. Leave unconnected.                                                             |

| 19, 21                    | MODN2,<br>MODN1 | Complementary Modulation Output with On-Chip Resistive Load. Connect to GND.                  |

| 20                        | MOD             | Modulation Output, DC-Coupled to EAM                                                          |

| 25                        | BIAS            | EAM Bias Output. Connect to the EAM via an inductor.                                          |

## Pin Description (continued)

| PIN | NAME    | FUNCTION                                                                                                                                                |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26  | BIASSET | Bias Current Set. Connected to the output of an external op amp (see Design Procedure).                                                                 |

| 27  | BIASMON | Bias Current Monitor. ( $V_{BIASMON} - V_{EE}$ ) / $7.5\Omega = I_{BIAS}$ .                                                                             |

| 31  | MODEN   | TTL/CMOS Modulation Enable Input. Low for normal operation, high to put the EAM in the absorption (logic 0) state. Internal $100k\Omega$ pullup to GND. |

| 32  | RTEN    | TTL/CMOS Data Retiming Input. Low for retimed data, high to bypass retiming latch. Internal $100k\Omega$ pullup to GND.                                 |

Figure 1. AC Characterization Circuit

## Detailed Description

The MAX3935 EAM driver consists of a high-speed modulation driver and an EAM-biasing block (see Figure 3). The clock and data inputs to the modulation driver interface with ECL and CML logic levels. The modulation and bias outputs sink current to VEE at -5.2V.

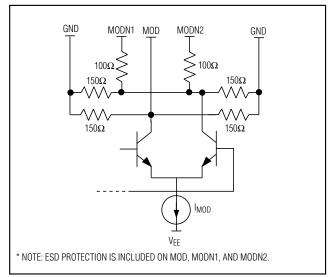

The modulation output stage is composed of a high-speed differential pair and a programmable current source with a maximum modulation current of 100mA. The rise- and fall-times are typically 34ps. The modulation current is designed to produce an EAM voltage up to 3.0Vp-p when driving a  $50\Omega$  module. The 3.0Vp-p

results from 100mA through 50 $\Omega$  in parallel with an internal 75 $\Omega$  resistor (30 $\Omega$ ).

Any loading of the EAM module with capacitance will degrade the optical output performance. Since the BIAS output is connected to the EAM, minimize the parasitic capacitance associated with this pad by using an inductor (L) to isolate the BIAS pin from the EAM.

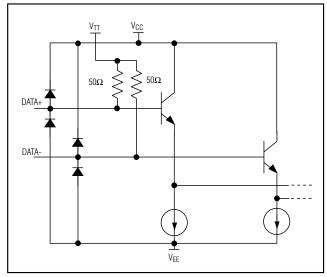

#### Clock/Data Input Logic Levels

The MAX3935 is directly compatible with 0V reference CML. Other logic interfaces are possible with AC-coupling capacitors. For 0V CML of AC-coupled logic, set VTT to 0V. For other DC-coupled differential signals, set VTT to the common-mode input voltage.

Figure 2. Required Input Signal, Setup/Hold-Time Definition and Output Polarity

#### **Optional Input Data Retiming**

To eliminate pattern-dependent jitter in the input data, a synchronous differential clock signal should be connected to the CLK+ and CLK- inputs, and the RTEN control input should be tied low. The input data is retimed on the rising edge of CLK+. If RTEN is tied high or left floating, the retiming function is disabled and the input data is directly connected to the output stage. Leave CLK+ and CLK- open when retiming is disabled.

#### **Pulse-Width Control**

The pulse-width control circuit can be used to minimize pulse-width distortion. The differential voltage between PWC+ and PWC- adjusts the pulse-width compensation. When PWC+ and PWC- are left open, the pulse-width control circuit is automatically disabled.

#### **Modulation Output Enable**

The MAX3935 inc<u>orporates</u> a modulation current enable input. When  $\overline{\text{MODEN}}$  is low, the modulation output (MOD) is enabled. When  $\overline{\text{MODEN}}$  is high or floating, the output is disabled. In the disabled condition, the modulation output sinks current to keep the EAM module in the high-absorption state. The typical EAM enable time is 2ns, and the typical disable time is 5ns.

#### **Current Monitors**

The MAX3935 features a bias-current monitor output (BIASMON) and a modulation-current monitor output

(MODMON). The voltage at BIASMON is equal to (IBIAS  $\times$  RBIAS) + VEE and the voltage at MODMON is equal to (IMOD  $\times$  RMOD) + VEE. IBIAS and IMOD are shown in Figure 3. The internal resistors RBIAS and RMOD are 7.5 $\Omega$  and 3 $\Omega$ , respectively (±10%). BIASMON and MODMON should be connected to the inverting input of an op amp to program the bias and modulation current (see *Design Procedure*).

### **Design Procedure**

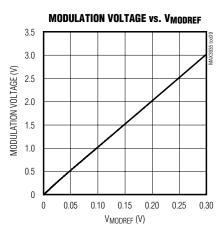

#### **Programming the Modulation Voltage**

The EAM modulation voltage results from I<sub>MOD</sub> passing through the EAM impedance in parallel with the internal  $75\Omega$ -termination resistor.

$$V_{MOD} \approx I_{MOD} \times \frac{Z_{EAM} \times 75\Omega}{Z_{EAM} + 75\Omega}$$

To program the desired modulation current, connect the inverting input of an op amp (see *Typical Application Circuit*) to MODMON and connect the output to MODSET. Connect the positive op amp voltage supply to ground and the negative supply to VEE. The modulation current is set by connecting a reference voltage VMODREF to the noninverting input of the op amp. Refer to the Modulation Voltage vs. VMODREF graph in the *Typical Operating Characteristics* to select the value of VMODREF that corresponds to the required modulation current.

$$I_{MOD} = \frac{V_{MODREF}}{3\Omega}$$

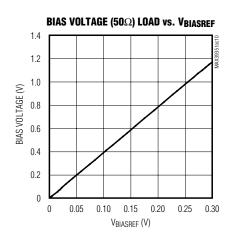

#### **Programming the Bias Voltage**

The EAM bias voltage results from IBIAS passing through the EAM impedance in parallel with the internal  $75\Omega$ -termination resistor.

$$V_{BIAS} \approx I_{BIAS} \times \frac{Z_{EAM} \times 75\Omega}{Z_{EAM} + 75\Omega}$$

To program the desired EAM bias current, connect the inverting input of an op amp (see *Typical Application Circuit*) to BIASMON and connect the output to BIASSET. Connect the positive op amp voltage supply to ground and the negative supply to VEE . The EAM bias current is set by connecting a reference voltage VBIASREF to the noninverting input of the op amp. Refer to the Bias Voltage vs. VBIASREF graph in the *Typical Operating Characteristics* to select the value of VBIAS that corresponds to the required EAM bias voltage.

Figure 3. Functional Diagram

$$I_{BIAS} = \frac{V_{BIASREF}}{7.5\Omega}$$

To keep the bias and modulation currents in compliance, the following constraint on the total current must be made for  $50\Omega$  EAM modules:

$$|V_{EE}| - (|B_{IAS} + |I_{MOD}) \times 30\Omega \ge 1.55V$$

#### **External Op Amp Selection**

External op amps are required for regulating the bias and modulation currents. The ability to operate from a single supply with input common-mode range extending to the negative supply rail is critical in the op amp selection. Low bias current and high PSRR are also important. Bias current to the inverting input passes through a  $5k\Omega$  resistor. This could add an error to the voltage produced by the modulation and bias current-sense resistors. The op amp gain bandwidth must be

high enough to regulate at the power-supply ripple frequency on  $\ensuremath{\text{V}_{\text{EE}}}.$

#### **Pulse-Width Control Setup**

Two methods of control are possible when pulse predistortion is desired to minimize distortion at the receiver. The pulse width may be set with a  $2k\Omega$  potentiometer (or equivalent fixed resistors) or by applying a voltage, with VEE + 1V common mode, to the PWC pins may set it. Refer to Table 1 for the desired effect of the pulse width setting.

**Table 1. Pulse-Width Control**

| PULSE<br>WIDTH | RP, RN for RP + RN = $2k\Omega$ | V <sub>PWC+</sub> , V <sub>PWC-</sub> for<br>V <sub>CM</sub> = V <sub>EE</sub> + 1V |

|----------------|---------------------------------|-------------------------------------------------------------------------------------|

| 100%           | 1k $\Omega$ or Open             | V <sub>PWC+</sub> = V <sub>PWC-</sub> = V <sub>EE</sub> + 1V                        |

| >100%          | RP > RN                         | V <sub>PWC+</sub> > V <sub>PWC-</sub>                                               |

| <100%          | RP < RN                         | VPWC+ < VPWC-                                                                       |

### **Applications Information**

#### **Layout Considerations**

To minimize loss and crosstalk, keep the connections between the MAX3935 output and the EAM module as short as possible. Use good high-frequency layout techniques and multilayer boards with uninterrupted ground plane to minimize EMI and crosstalk. Circuit boards should be made using low-loss dielectrics. Use controlled-impedance lines for the clock and data inputs as well as the modulation output.

### Pin Configuration

#### **Input and Output Schematics**

Figure 4. Equivalent Input Circuit

Figure 5. Equivalent Output Circuit

### **Chip Information**

TRANSISTOR COUNT: 1535

SUBSTRATE: SOI

PROCESS: BIPOLAR SILICON GERMANIUM

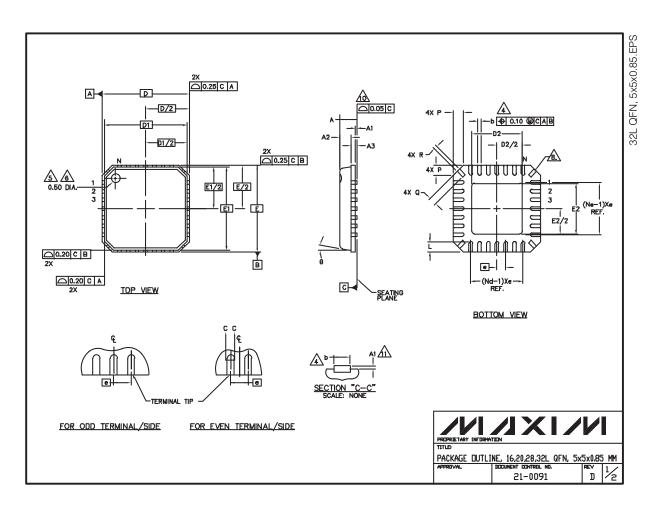

## **Package Information**

### Package Information (continued)

MIN

#### **NOTES:**

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM)

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

- 3. N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

MINIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

5. THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE

$\wedge$  Package by using indentation mark or other feature of Package body.

6 EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

7. ALL DIMENSIONS ARE IN MILLIMETERS.

A THE SHAPE SHOWN ON FOUR CORNERS ARE NOT ACTUAL I/O.

9. PACKAGE WARPAGE MAX 0.05mm.

APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDING PART OF EXPOSED

PAD FROM MEASURING.

APPLIED ONLY FOR TERMINALS.

| 2 × 2 m    | PITCH     | VARIAT      |            | N <sub>D</sub> | ,85"       | PITCH    | VARIA      |           | N <sub>a</sub> | 5 y 3 m | PITCH      | VARIA      |              | "o. | \$ Y W | PITCH    | VARIA     |               | N <sub>D</sub> |

|------------|-----------|-------------|------------|----------------|------------|----------|------------|-----------|----------------|---------|------------|------------|--------------|-----|--------|----------|-----------|---------------|----------------|

| <u>ا</u> ا | MIN.      | NOM.        | MAX.       | TE.            | ૧          | MIN.     | I NOM.     | I MAX.    | 'ε             | ા       | MIN.       | NOM.       | I MAX.       | Ι'ε | ା ଅ    | MIN.     | I NOM.    | MAX.          | T <sub>E</sub> |

| e          |           | 0.80 BSC    | ;          |                | 9          |          | 0.65 BSC   | :         |                | e       |            | 0.50 BSC   | ;            |     |        |          | 0.50 BSC  | ;             |                |

| N          |           | 16          |            | 3              | N          |          | 20         |           | 3              | N       |            | 28         |              | 3   | N      |          | 32        |               | 3              |

| Nd         |           | 4           |            | 3              | Nd         |          | 5          |           | 3              | Nd      |            | 7          |              | 3   | Nd     |          | 8         |               | 3              |

| Ne         |           | 4           |            | 3              | Ne         |          | 5          |           | 3              | Ne      |            | 7          |              | 3   | Ne     |          | 8         |               | 3              |

|            | 0.50      | 0.60        | 0.75       |                | L          | 0.50     | 0.60       | 0.75      |                |         | 0.50       | 0.60       | 0.75         |     | ш      | 0.30     | 0.40      | 0.55          |                |

| ь          | 0.28      | 0.33        | 0.40       | 4              | Ь          | 0.23     | 0.28       | 0.35      | 4              | Ы       | 0.18       | 0.23       | 0.30         | 4   | ь      | 0.18     | 0.23      | 0.30          | 4              |

| Q          | 0.30      | Ω.40        | 0.65       |                | Q          | 0.30     | 0.40       | 0.65      |                | Q       | 0.30       | 0.40       | 0.65         |     | Q      | 0.00     | 0.20      | 0.45          |                |

| D2         | SEE EXPOS | SED PAD VA  | RIATION: B |                | D2         | SEE EXPO | SED PAD VA | RIATION:B |                | D2      | SEE EXPOSI | ED PAD VA  | RIATION: A.B |     | D2     | SEE EXPO | SED PAD V | ARIATION: A   |                |

| E2         | SEE EXPOS | RETO PAR VA | PIATION-B  |                | <b>E</b> 2 | SEE EXBU | SED BAD VA | DIATION+D |                | E2      | SEE EXBOSI | EN BAN VAL | SIATION+ A R |     | E2     | SEE EXBU | GEN BAN V | A PIATION - A |                |

| SYMBOLS     |   |      | D2   |      |      | E2   |      | NOTE |

|-------------|---|------|------|------|------|------|------|------|

|             |   | MIN  | NOM  | MAX  | MIN  | NOM  | MAX  |      |

| EXPOSED PAD | Α | 2.95 |      |      | 2.95 | 3.10 | 3.25 |      |

| VARIATIONS  |   | בב   | 0.70 | 0.00 | 0.55 | 0.70 | 0 05 |      |

EXAMPLE: WE CAN CALL VARIATION "BB" FOR 20 TERMINAL QFN WITH 2.70mm X 2.70mm NOMINAL EXPOSED PAD DIMENSION. THE FORMER ONE IN VARIATION IS FOR PITCH VARIATION AND THE LETTER ONE IS FOR EXPOSED PAD VARIATION.

|   | PROPROETARY INFORMA |                          |        |    |

|---|---------------------|--------------------------|--------|----|

| 1 | TTTLE               |                          |        |    |

|   | PACKAGE DUTLI       | NE, 16,20,28,32L QFN, 5x | 5x0.85 | MM |

| 1 | APPROVAL            | DOCUMENT CONTROL NO.     | REV    | 2/ |

|   |                     | 21-0091                  | D      | 72 |

Maxim makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Maxim assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "typicals" must be validated for each customer application by customer's technical experts. Maxim products are not designed, intended or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Maxim product could create a situation where personal injury or death may occur.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600